# A New Cascaded Multilevel Inverter with Minimal Number of Switches

<sup>1</sup>N. Harsha Vardhan Reddy, <sup>2</sup>K. Rajith, <sup>3</sup>G. Mounika <sup>1, 3</sup>PG Student, EEE, DVR College of Engineering, Hyderabad, <u>harshareddynarva9652@gmail.com</u> <sup>2</sup>PG Student, EEE, RGMCET, Nandyal, rajji4309@gmail.com

Abstract: In recent technologies the multilevel inverters are exceptionally used in moderate and significant power applications considering their eminent operation characteristics. Primarily, the operating level of MLI's is subjected to number of levels generated in output voltage. Basically, the topologies of multilevel inverter are categorized as diode clamped, cascaded H-Bridge & flying capacitor, on comparing performance characteristics CMLI is preferred because of its standardized characteristics. However the conventional CMLI has considerable defects comparatively employs a sole DC source and requires the larger number of switching devices. Likely effects will boosted when there is increment in number of levels. But in this particular article, an advanced elementary block is recommended for obtaining more number of output levels together with fewer number of switching components. For acquiring the required number of output levels, altogether cascading the considerable elementary blocks in series. In addition to that the proposed MLI design has proficiency to generate only positive voltage levels. Apart from +ve levels to generate -ve levels, a unique H- bridge circuit is employed. Considering the amplitude of DC source four distinct principles are designed to obtain the required number of output levels. By comparing the proposed CHBMLI with the conventional CMLI, the proposed algorithm has superlative design with minimal operation of driver circuits, DC voltage sources and power switches. The designed algorithm is simulated in MATLAB / SIMULINK.

Keywords: Multilevel inverters, CHBMLI and CMLI.

### I. INTRODUCTION

Multilevel Inverters (MLI's) has grabbed significant attention in power industry, as MLI's are predominately operating in moderate and greater power applications likely UPS, large induction motor drives, HVDC and FACTS transmission systems etc., [1-6] MLI's can comfortably generates the required output voltage levels using only single or number of input DC sources.

Generated output waveform shape depends on number of output levels. Comparing with the basic 2 level voltage source inverter, MLI's are mostly preferred because of its performance like lesser voltage stress, minimized THD and reduced switching losses. Based on number of input DC sources these MLI's are categorized into different topologies, namely Diode Clampled Multi Level Inverter (DCMLI), Flying Capacitor Multi Level Inverter (FCMLI) and Cascaded H- Bridge Multi Level Inverter (CMLI). Among the three topologies CMLI's are mostly preferred because of its simplicity, modularity, doesn't require any clamping diodes and reliability

Further CMLI are categorized as symmetrical CMLI's & asymmetrical CMLI's, These CMLI's are differentiated by magnitudes of input DC sources. Hence the magnitudes of DC sources are identical in case of symmetrical CMLI where as for asymmetrical CMLI's the magnitudes of DC sources are different. The number of output levels generated more in asymmetrical CMLI than that of symmetrical CMLI. Foremost the asymmetrical CMLI's are apt for PV applications. However in asymmetrical CMLIs switching components has distinct ratings.

This article demonstrates both symmetrical and asymmetrical arrangements. The designed CMLI has ability to operate in symmetrical as well as asymmetrical arrangement. Articles [13]-[19] demonstrate distinct CMLI topologies performed as symmetrical configuration. On comparing with the proposed topology, few standard topologies demonstrated in these articles comprise DC sources, diodes and high number of switching elements.

At present an advanced elementary block is designed to generate greater number of output levels accompanied by fewer number of switching elements. For acquiring the required number of output levels, altogether cascading the considerable elementary blocks in series. In addition to that the proposed MLI design has proficiency to generate only positive voltage levels. Apart from +ve levels to generate –ve levels, a unique H- bridge circuit is employed. Considering the amplitude of DC source four distinct principles are designed to obtain the required number of output levels. The proposed CHBMLI has superlative design when compare to conventional CMLI.

Further sections of this article present the performance analysis: here section 2 demonstrates the proposed topography. Section 3 demonstrates the comparative analysis proposed CHBMLI with the conventional CMLI. Section 4 presents the analysis of proposed technologies. Likely next section conclude following with the simulation analysis.

## II. PROPOSED TOPOLOGY

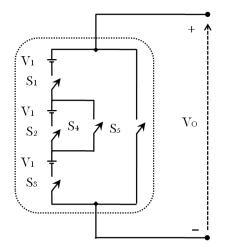

The proposed elementary block comprises of three DC voltage sources and five switching components cascaded according to fig. 1. This designed fundamental block generates 3 positive levels essentially 0,  $(V_1 + V_3)$ ,  $(V_1 + V_2 + V_3)$  and no negative voltage levels are generated at output. As elementary block comprises of five switching components, their status is together tabulated in table I. For acquiring the required number of output levels, altogether cascading the considerable elementary blocks in series.

Table I. Switching Pattern for Proposed Basic Unit

| No of levels |       | Swit  | $V_0$                 |                       |                       |                   |

|--------------|-------|-------|-----------------------|-----------------------|-----------------------|-------------------|

|              | $S_1$ | $S_2$ | <b>S</b> <sub>3</sub> | <b>S</b> <sub>4</sub> | <b>S</b> <sub>5</sub> | <b>V</b> 0        |

| 1            | 0     | 0     | 0                     | 0                     | 1                     | 0                 |

| 2            | 1     | 0     | 1                     | 1                     | 0                     | $V_1 + V_3$       |

| 3            | 1     | 1     | 1                     | 0                     | 0                     | $V_1 + V_2 + V_3$ |

Fig.1 Elementary Block

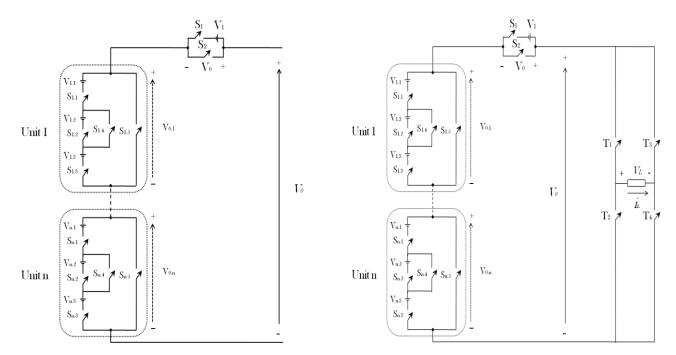

The designed architecture is unable to generate  $V_1$  level. To obtain the missing output levels (assuming the amplitude of  $V_1 = V_{dc}$  i.e., same as minimum output level) the secondary unit is cascaded in series to fundamental block. This secondary unit comprises the switching components  $(S_1, S_2)$  and one DC voltage source which is cascaded in series with fundamental block, the conjunction of fundamental block and secondary unit represents the MLI structure which is displayed as fig. 2. The derived output voltage  $v_0$  of fundamental block and secondary unit is represented as:

$$V_{O}(t) = V_{01}(t) + V_{02}(t) + V_{03}(t) + \dots + V_{0n}(t) + V_{1}(t)$$

(1)

Fig.2 Proposed MLI Structure

Fig.3 Proposed CHBMLI Structure

Generated output  $S_1$  $S_{1,2}$  $S_{1,5}$  $S_{2,4}$  $S_2$  $S_{1,1}$  $S_{1,3}$  $S_{1,4}$  $S_{2,1}$  $S_{2,2}$  $S_{2,3}$  $S_{2,5}$  $S_{n,1}$  $S_{n,2}$  $S_{n,3}$ Sn,4  $S_{n,5}$ Voltage (vo)  $V_1$  $V_{1,1} \!\!+\! V_{1,3}$ . . .  $V_{1.1} + V_{1.2} + V_{1.3}$  $V_{2,1} + V_{2,3}$  $V_{2,1} \!\!+\! V_{2,2} \!\!+\! V_{2,3}$  $V_{1,1}+V_{2,1}+V_{3,1}+$  $V_{1,2} + V_{3,2}$  $V_{1,1}+V_{2,1}+V_{3,1}+$  $V_{1,2}+V_{2,2}+V_{3,2}$ . . . . . . . . . . . . . . . .  $\sum V_{i,1} + V_{i,2} + V_{i,3}$ For j=1,2,3,....nV1+∑  $V_{i,1}+V_{i,2}+V_{i,3}$  For i=1,2,3,....n

Table II. Generated Output Voltage Based on the States Power Switches

The switching component status and their corresponding output levels of MLI structure are tabulated in table II. This MLI structure generates only positive voltage levels. In order to attain both +ve and -ve levels, a single H-bridge circuit is used. This topology is stated as Proposed CHBMLI which is displayed as Fig.3.

Finally the number of switches "N<sub>switch</sub>" and number of dc voltage sources "N<sub>source</sub>" consider for the proposed new CHBMLI's are represented as:

$$N_{\text{Switch}} = 5n + 6 \tag{2}$$

$$N_{\text{Source}} = 3n + 1 \tag{3}$$

Where n is the number of basic units connected in series.

This article demonstrates on both symmetrical and asymmetrical configurations. The proposed CMLI has ability to perform as symmetrical and asymmetrical configuration. Considering the amplitude of DC source four distinct principles are designed to obtain the required number of output levels. By comparing the proposed CHBMLI with the conventional CMLI, the proposed algorithm has superlative design. Number of output levels and their corresponding algorithms are tabulated in table III. The magnitudes of all DC voltage sources are identical in first algorithm but for remaining algorithms the magnitudes are not identical. Hence all proposed algorithms except the first are considered as an asymmetric CMLI's.

Table III. Proposed Algorithms and their Parameters, Where N= Number of Basic Units.

| Proposed algorithm                | Magnitude of dc voltage sources                                                                                                                           | Number of levels (m)   | Peak<br>Vo                                   |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------------------------|

| First algorithm(P <sub>1</sub> )  | $V_{j,1} = V_{j,2} = V_{j,3} = V_{dc}$ , For j=1,2,,n                                                                                                     | 6n+3                   | (3n+1) V <sub>dc</sub>                       |

| Second algorithm(P <sub>2</sub> ) | $V_{1,1} = V_{1,2} = V_{1,3} = V_{dc}$ and $V_{j,1} = V_{j,2} = V_{j,3} = 2V_{dc}$ For $j = 2,3,,n$                                                       | 12n-3                  | (6n-2) V <sub>dc</sub>                       |

| Third algorithm(P <sub>3</sub> )  | $\begin{aligned} V_{1,1} &= V_{1,2} = V_{1,3} = V_{dc} \\ V_{j,1} &= (1/3)V_{j,2} = V_{j,3} = \ (3^{j-2})V_{dc} \\ \text{for } j &= 2,3,,n \end{aligned}$ | 5(3 <sup>n-1</sup> )+4 | [(5(3 <sup>n-1</sup> )+3)/2] V <sub>dc</sub> |

| Fourth algorithm(P4)              | $V_{j,1} = 0.5 \ V_{j,2} = V_{j,3} = \ (2^{j-1}) V_{dc}$ For $j=1,2,,n$                                                                                   | 2 <sup>n+3</sup> -5    | $(2^{n+2}-3) V_{dc}$                         |

Moreover, based on equations of maximum output voltage and its amplitude, Asymmetrical CMLI produces more no. of output levels that of symmetrical CMLI by considering identical no. of switching elements and DC voltage sources.

# III. COMPARING THE PROPOSED TOPOLOGY WITH CONVENTIONAL TOPOLOGIES

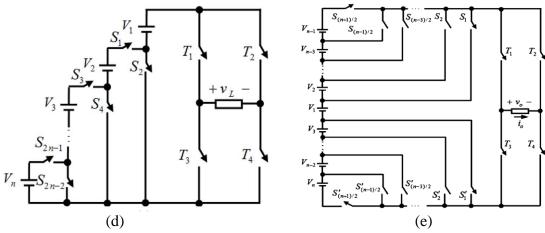

Major purpose of suggested CHBMLI is to produce more no. of output steps with minimal no. of switches. . Comparison is accomplished between the suggested CHBMLI and traditional CMLIs in terms of driver circuits, power switches & dc voltage sources.

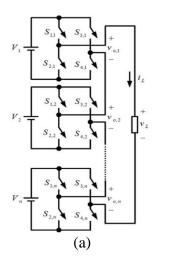

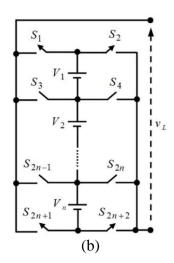

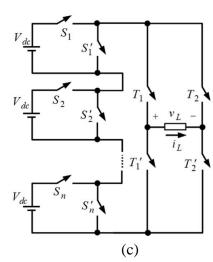

Fig.4 Different CMLI Topologies (a) Reported in [14], (b) Reported in [15], (c) Reported in [16], (d) Reported in [17], (e) Reported in [18].

In this comparison, different algorithms for proposed CHBMLI are represented by  $P_1$ - $P_4$ , respectively and different traditional CMLI's published in [14]-[18] are considered. The above mentioned CMLI's entire are indicated Fig. 4.

Table IV. Components Required Comparison between Conventional CMLI and Proposed CHBMLI

| Converter<br>Type         | Conventional CMLI published |                   |                   |                   | ed                | Proposed CHBMLI with algorithms             |                                             |                                                                    |                                                                   |

|---------------------------|-----------------------------|-------------------|-------------------|-------------------|-------------------|---------------------------------------------|---------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------|

| Parameter                 | [14]                        | [15]              | [16]              | [17]              | [18]              | P1                                          | P2                                          | Р3                                                                 | P4                                                                |

| Main<br>Switches<br>Count | 2(m-1)                      | (m+1)             | (m+3)             | (m+1)             | (m+3)             | $5\left(\frac{(m-3)}{6}\right)+6$           | $5\left(\frac{(m-3)}{12}\right)+6$          | $5\left[\frac{\left(\log\frac{3(m-4)}{5}\right)}{\log 3}\right]+6$ | $5\left[\frac{\left(\log(\frac{m+5}{8})\right)}{\log 2}\right]+6$ |

| No. of<br>Sources         | $\frac{(m-1)}{2}$           | $\frac{(m-1)}{2}$ | $\frac{(m-1)}{2}$ | $\frac{(m-1)}{2}$ | $\frac{(m-1)}{2}$ | $\left(\frac{\left(m-3\right)}{2}\right)+1$ | $\left(\frac{\left(m-3\right)}{4}\right)+1$ | $3\left[\frac{\left(\log\frac{3(m-4)}{5}\right)}{\log 3}\right]+1$ | $3\left[\frac{\left(\log(\frac{m+5}{8})\right)}{\log 2}\right]+1$ |

The table IV illustrates comparison of components requirement of a single phase proposed verses conventional topology to produce "m" level of output voltage.

Fig.5 Number of Switches Required for m Level

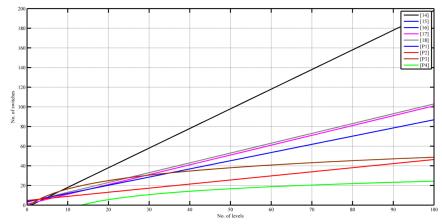

Based on table IV, Fig. 6 clearly compares the no. of DC voltage sources of proposed topology to traditional CMLIs, It is noticeable that the no. of DC voltage sources required for developed inverter

are lesser than that of other existing inverters. This variation will be higher on considering the fourth proposed algorithm.

Fig.6 Number of Sources Required for m Level

## IV. MODULATION TECHNIQUES

In major industrial applications, the output voltages of inverters need to be varied. The appearance of MLI's depends on switching schemes used for developing PWM signals.

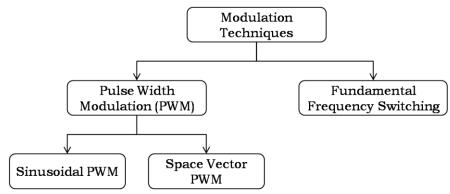

Fig.7 Types of PWM Schemes

Fig.7 shows different modulation schemes. Out of these spwm scheme is more preferrable for MLIs due to its merits. Level shift and phase shift PWM schemes are another classification of SPWM scheme. In this paper the different level shifted PWM techniques are considered likely In Phase Disposition (IPD), Phase Opposition Disposition (POD) and Alternative Phase Opposition Disposition (APOD) are considered.

# V. SIMULATION RESULTS

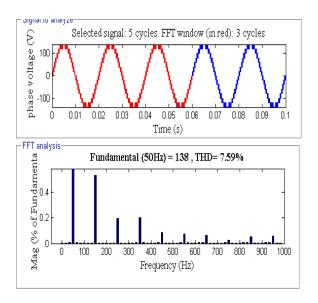

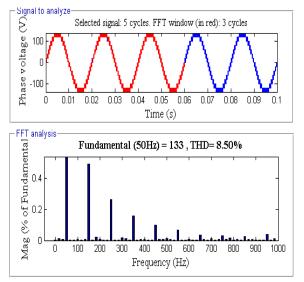

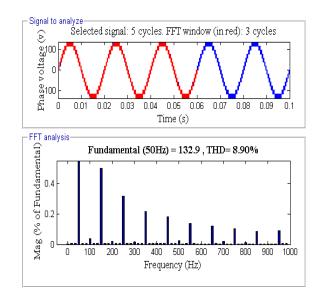

The implementation of proposed CHBMLI with two elementary blocks by different level shift SPWM schemes established through MATLAB simulation. The suggested CMLI is able to operate both symmetrical and asymmetrical configuration. This script reveals four different algorithms based on amplitudes of DC sources for achieving desired no. of output levels. The simulation results are validated for four different algorithms.

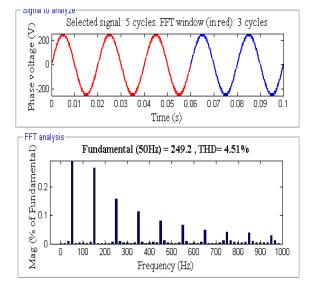

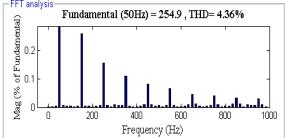

The simulated values are as follows: Input voltage 20V, Carrier frequency 100 kHz, Reference frequency 50 Hz, Modulation Index = 0.96. Table V shows the % of THD obtained with different carrier distribution with proposed algorithm. It is observed that the % of THD obtained with P4 algorithm is as per IEEE standards.

Table V. % of THD Obtained by Different Algorithm

|           | P1    | P2   | P3   | P4   |  |  |  |

|-----------|-------|------|------|------|--|--|--|

| Technique | % THD |      |      |      |  |  |  |

| APOD      | 8.80  | 5.96 | 6.66 | 4.51 |  |  |  |

| IPD       | 8.92  | 5.95 | 6.66 | 4.51 |  |  |  |

| POD       | 8.81  | 5.95 | 6.65 | 4.54 |  |  |  |

From fig.8 to fig.10 shows fundamental output voltage and % THD for P1 algorithm using different level shift modulation schemes.

Fig.8 P1 Algorithm Output Voltage using APOD-PWM

Fig.10 P1 Algorithm Output Voltage using POD-PWM

Fig.9 P1 Algorithm Output Voltage using PD-PWM

Fig.11 P4 Algorithm Output Voltage using APOD-PWM

From fig.11 to fig.13 shows fundamental output voltage and % THD for P4 algorithm using different level shift modulation schemes

Fig.12 P4 Algorithm Output Voltage using PD-PWM

Fig.13 P4 Algorithm Output Voltage using POD-PWM

### VI. CONCLUSION

Comparison is accomplished between the Proposed CHBMLI and the conventional CMLI. Utilization of no. of switches and DC sources are lower in Proposed CHBMLI compare to earlier CMLIs discussed in this script. Fourth algorithm gives higher output voltage and lower THD than remaining algorithms with same no. of switches and driver circuits. It is conclusive that the suggested model is finest in terms of lesser usage of switches, driver circuits, and DC sources. Suggested CHBMLI can be designed for real time applications due to its features.

### **REFERENCES**

- [1] B. Wu, High-power converters and AC drives: John Wiley & Sons, 2006.

- [2] J. Rodriguez, J.-S. Lai, and F. Z. Peng, "Multilevel inverters: a survey of topologies, controls, and applications," *Industrial Electronics, IEEE Transactions on*, vol. 49, pp. 724-738, 2002.

- [3] J. Rodriguez, S. Bernet, W. Bin, J. O. Pontt, and S. Kouro, "Multilevel Voltage-Source-Converter Topologies for Industrial Medium-Voltage Drives," *Industrial Electronics, IEEE Transactions on*, vol. 54, pp. 2930-2945, 2007.

- [4] M. Malinowski, K. Gopakumar, J. Rodriguez, Pe, x, and M. A. rez, "A Survey on Cascaded Multilevel Inverters," *Industrial Electronics, IEEE Transactions on*, vol. 57, pp. 2197-2206, 2010.

- [5] J. Rodriguez, S. Bernet, P. K. Steimer, and I. E. Lizama, "A Survey on Neutral-Point-Clamped Inverters," *Industrial Electronics, IEEE Transactions on*, vol. 57, pp. 2219-2230, 2010.

- [6] P. Qashqai, A. Sheikholeslami, H. Vahedi, and K. Al-Haddad, "A Review on Multilevel Converter Topologies for Electric Transportation Applications," in *Vehicle Power and Propulsion Conference (VPPC)*, 2015 IEEE, 2015, pp. 1-6.

- [7] R. Teichmann and S. Bernet, "A comparison of three-level converters versus two-level converters for low-voltage drives, traction, and utility applications," *IEEE Trans. Ind. Appl.*, vol. 41, no. 3, pp. 855–865, May/Jun. 2005.

- [8] O. Alonso, P. Sanchis, E. Gubia, L. Marroyo, "Cascaded H-bridge multilevel converter for grid connected photovoltaic generators with independent maximum power point tracking of each solar array", *Proc. 34th Annu. IEEE PESC*, vol. 2, pp. 731-735, 2003-Jun.

- [9] N. Farokhnia, S. H. Fathi, N. Yousefpoor, and M. K. Bakhshizadeh, "Minimizations of total harmonic distortion in a cascaded multilevel inverter by regulating of voltages DC sources," *IET Power Electron.*, vol. 5, no. 1, pp. 106–114, Jan. 2012.

- [10] S. Laali, K. Abbaszades, and H. Lesani, "A new algorithm to determine the magnitudes of DC voltage sources in asymmetrical cascaded multilevel converters capable of using charge balance control methods," in *Proc. ICEMS*, Incheon, Korea, 2010, pp. 56–61.

- [11] S. Laali, K. Abbaszadeh, and H. Lesani, "Control of asymmetric cascaded multilevel inverters based on charge balance control methods," *Int. Rev. lect. Eng.*, vol. 6, no. 2, pp. 522–528, Mar./Apr. 2011.

- [12] E. Babaei and S. H. Hosseini, "Charge balance control methods for asymmetrical cascade multilevel converters," in *Proc. ICEMS*, Seoul, Korea, 2007, pp. 74–79

- [13] Y. Hinago and H. Koizumi, "A single-phase multilevel inverter using switched series/parallel DC voltage sources," *IEEE Trans. Ind. Electron.* vol. 57, no. 8, pp. 2643–2650, Aug. 2010.

- [14] M. Manjrekar and T. A. Lipo, "A hybrid multilevel inverter topology for drive application," in *Proc. APEC*, 1998, pp. 523–529.

- [15] E. Babaei, S. H. Hosseini, G. B. Gharehpetian, M. Tarafdar Haque, and M. Sabahi, "Reduction of dc voltage sources and switches in asymmetrical multilevel converters using a novel topology," *Elect. Power Syst. Res.*, vol. 77, no. 8, pp. 1073–1085, Jun. 2007.

- [16] E. Babaei and S. H. Hosseini, "New cascaded multilevel inverter topology with minimum number of switches," *J. Energy Convers. Manage.*, vol. 50, no. 11, pp. 2761–2767, Nov. 2009.

- [17] W. K. Choi and F. S. Kang, "H-bridge based multilevel inverter using PWM switching function," in *Proc. INTELEC*, 2009, pp. 1–5.

- [18] M. F. Kangarlu, E. Babaei, and S. Laali, "Symmetric multilevel inverter with reduced components based on non-insulated DC voltage sources," *IET Power Electron.*, vol. 5, no. 5, pp. 571–581, May 2012.

- [19] G. Waltrich and I. Barbi, "Three-phase cascaded multilevel inverter using power cells with two inverter legs in series," *IEEE Trans. Ind. Appl.*, vol. 57, no. 8, pp. 2605–2612, Aug. 2010.